- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Chất mang wafer phủ CVD TaC

Là nhà sản xuất và nhà máy sản xuất sản phẩm tấm wafer phủ CVD TaC chuyên nghiệp tại Trung Quốc, VeTek Semiconductor CVD TaC Coating wafer Carrier là một công cụ mang wafer được thiết kế đặc biệt cho môi trường ăn mòn và nhiệt độ cao trong sản xuất chất bán dẫn. Sản phẩm này có độ bền cơ học cao, khả năng chống ăn mòn và ổn định nhiệt tuyệt vời, mang lại sự đảm bảo cần thiết cho việc sản xuất các thiết bị bán dẫn chất lượng cao. Yêu cầu thêm của bạn đều được chào đón.

Gửi yêu cầu

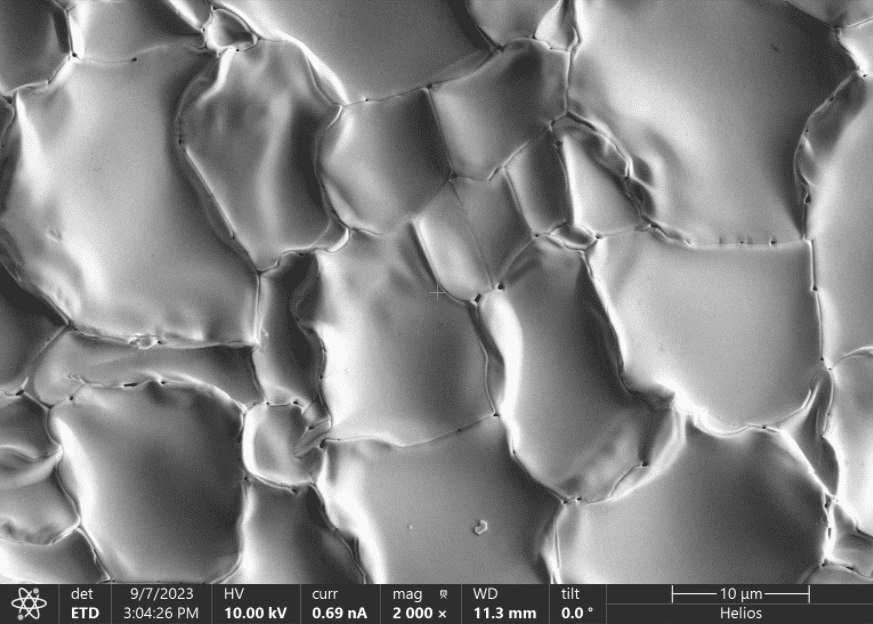

Trong quá trình sản xuất chất bán dẫn, VeTek SemiconductorChất mang wafer phủ CVD TaClà một cái khay dùng để đựng bánh xốp. Sản phẩm này sử dụng quy trình lắng đọng hơi hóa học (CVD) để phủ một lớp Lớp phủ TaC lên bề mặt của sản phẩm.Chất nền mang wafer. Lớp phủ này có thể cải thiện đáng kể khả năng chống oxy hóa và ăn mòn của chất mang bán dẫn, đồng thời giảm ô nhiễm hạt trong quá trình xử lý. Nó là một thành phần quan trọng trong xử lý chất bán dẫn.

Chất bán dẫn VeTekChất mang wafer phủ CVD TaCbao gồm một chất nền và mộtlớp phủ tantalum cacbua (TaC).

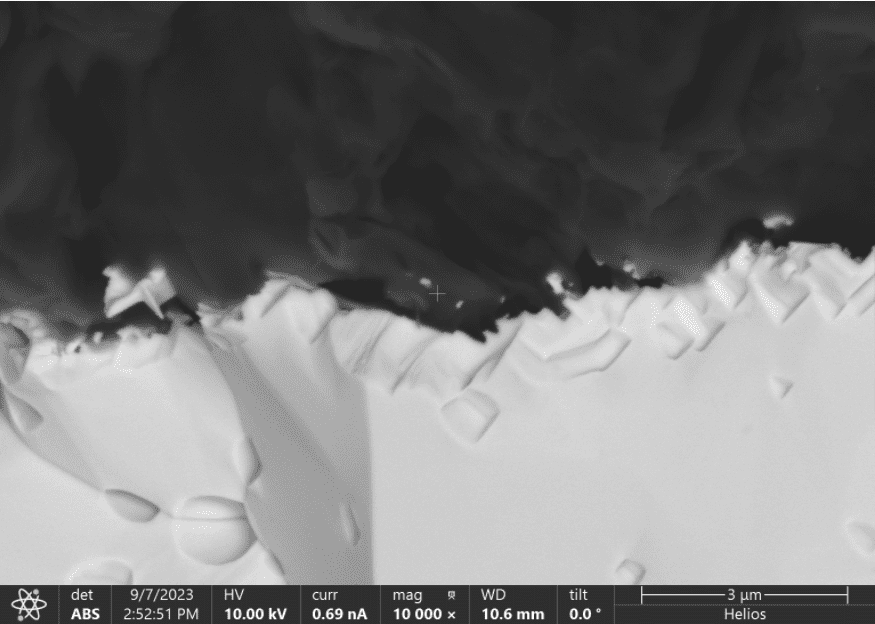

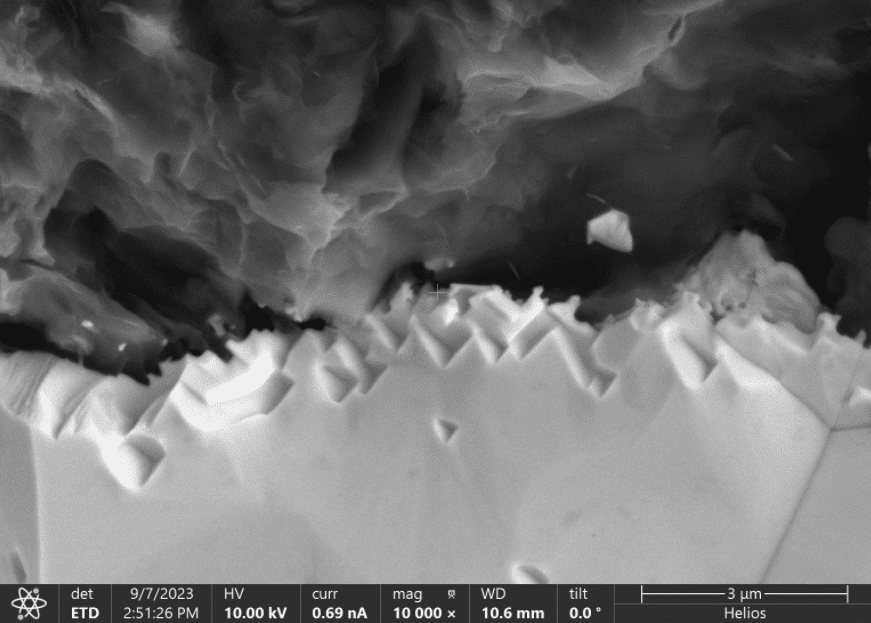

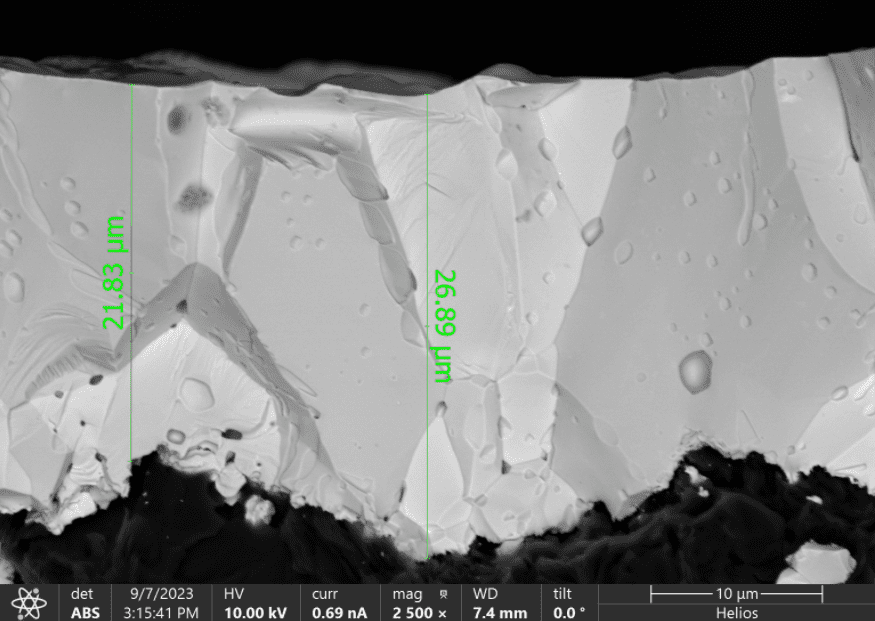

Độ dày của lớp phủ cacbua tantalum thường nằm trong phạm vi 30 micron và TaC có điểm nóng chảy cao tới 3.880°C đồng thời mang lại khả năng chống ăn mòn và mài mòn tuyệt vời cùng nhiều đặc tính khác.

Vật liệu cơ bản của vật mang được làm bằng than chì có độ tinh khiết cao hoặccacbua silic (SiC), sau đó một lớp TaC (độ cứng Knoop lên tới 2000HK) được phủ lên bề mặt thông qua quy trình CVD để cải thiện khả năng chống ăn mòn và độ bền cơ học.

Chất mang wafer phủ CVD TaC của VeTek Semiconductor thườngđóng các vai trò sau trong quá trình mang wafer:

Tải và cố định wafer: Độ cứng knoop của cacbua tantalum cao tới 2000HK, có thể đảm bảo hiệu quả sự hỗ trợ ổn định của wafer trong buồng phản ứng. Kết hợp với độ dẫn nhiệt tốt của TAC (độ dẫn nhiệt là khoảng 21 w/mk), nó có thể làm cho bề mặt wafer được làm nóng đều và duy trì sự phân bố nhiệt độ đồng đều, giúp đạt được sự tăng trưởng đồng đều của lớp epiticular.

Giảm ô nhiễm hạt: Bề mặt nhẵn và độ cứng cao của lớp phủ CVD TaC giúp giảm ma sát giữa chất mang và tấm bán dẫn, từ đó giảm nguy cơ nhiễm bẩn hạt, vốn là chìa khóa để sản xuất các thiết bị bán dẫn chất lượng cao.

Độ ổn định nhiệt độ cao: Trong quá trình xử lý chất bán dẫn, nhiệt độ vận hành thực tế thường nằm trong khoảng từ 1.200°C đến 1.600°C và lớp phủ TaC có điểm nóng chảy cao tới 3.880°C. Kết hợp với hệ số giãn nở nhiệt thấp (hệ số giãn nở nhiệt xấp xỉ 6,3 × 10⁻⁶/°C), chất mang có thể duy trì độ bền cơ học và độ ổn định kích thước trong điều kiện nhiệt độ cao, ngăn tấm bán dẫn bị nứt hoặc biến dạng ứng suất trong quá trình xử lý.

Lớp phủ tantalum cacbua (TaC) trên mặt cắt cực nhỏ:

Tính chất vật lý cơ bản của lớp phủ CVD TaC:

Tính chất vật lý của lớp phủ TaC

Tỉ trọng

14,3 (g/cm³)

Độ phát xạ cụ thể

0.3

Hệ số giãn nở nhiệt

6,3*10-6/K

Độ cứng (HK)

2000 HK

Sức chống cự

1×10-5 Ôm*cm

Độ ổn định nhiệt

<2500oC

Thay đổi kích thước than chì

-10~-20um

độ dày lớp phủ

≥20um giá trị điển hình (35um±10um)