- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Giải thích đầy đủ về quy trình sản xuất chip (1/2): từ tấm bán dẫn đến đóng gói và thử nghiệm

2024-09-18

Việc sản xuất mỗi sản phẩm bán dẫn đòi hỏi hàng trăm quy trình và toàn bộ quy trình sản xuất được chia thành 8 bước:chế biến wafer - quá trình oxy hóa - quang khắc - khắc - lắng đọng màng mỏng - sự kết nối - thử nghiệm - bao bì.

![]()

Bước 1:Chế biến wafer

Mọi quá trình bán dẫn đều bắt đầu từ một hạt cát! Bởi vì silicon có trong cát là nguyên liệu thô cần thiết để sản xuất tấm wafer. Tấm wafer là những lát tròn được cắt từ các ống trụ đơn tinh thể làm bằng silicon (Si) hoặc gallium arsenide (GaAs). Để chiết xuất vật liệu silicon có độ tinh khiết cao cần có cát silic, một loại vật liệu đặc biệt có hàm lượng silicon dioxide lên tới 95%, cũng là nguyên liệu chính để chế tạo tấm wafer. Gia công wafer là quá trình tạo ra các wafer trên.

đúc phôi

Đầu tiên, cát cần được nung nóng để tách carbon monoxide và silicon trong đó, và quá trình này được lặp lại cho đến khi thu được silicon loại điện tử có độ tinh khiết cực cao (EG-Si). Silicon có độ tinh khiết cao tan chảy thành chất lỏng và sau đó đông đặc lại thành dạng rắn đơn tinh thể, được gọi là "phôi", đây là bước đầu tiên trong sản xuất chất bán dẫn.

Độ chính xác chế tạo của thỏi silicon (trụ silicon) rất cao, đạt đến mức nanomet và phương pháp sản xuất được sử dụng rộng rãi là phương pháp Czochralski.

Cắt phôi

Sau khi hoàn thành bước trước, cần dùng cưa kim cương cắt bỏ hai đầu phôi rồi cắt thành những lát mỏng có độ dày nhất định. Đường kính của miếng phôi xác định kích thước của wafer. Các tấm wafer lớn hơn và mỏng hơn có thể được chia thành các đơn vị có thể sử dụng được nhiều hơn, giúp giảm chi phí sản xuất. Sau khi cắt phôi silicon, cần đánh dấu “vùng phẳng” hoặc “vết lõm” trên lát cắt để thuận tiện cho việc thiết lập hướng xử lý làm chuẩn ở các bước tiếp theo.

Đánh bóng bề mặt wafer

Các lát cắt thu được thông qua quá trình cắt ở trên được gọi là "tấm bán dẫn trần", tức là "tấm bán dẫn thô" chưa qua chế biến. Bề mặt của tấm bán dẫn trần không đồng đều và không thể in trực tiếp mẫu mạch lên đó. Do đó, trước tiên cần loại bỏ các khuyết tật bề mặt thông qua quá trình mài và ăn mòn hóa học, sau đó đánh bóng để tạo thành bề mặt nhẵn, sau đó loại bỏ các chất ô nhiễm còn sót lại thông qua quá trình làm sạch để thu được tấm wafer thành phẩm có bề mặt sạch.

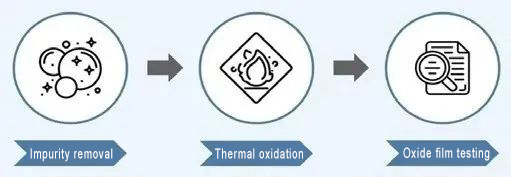

Bước 2: Quá trình oxy hóa

Vai trò của quá trình oxy hóa là tạo thành một lớp màng bảo vệ trên bề mặt tấm wafer. Nó bảo vệ tấm bán dẫn khỏi các tạp chất hóa học, ngăn dòng điện rò rỉ đi vào mạch, ngăn chặn sự khuếch tán trong quá trình cấy ion và ngăn tấm bán dẫn bị trượt trong quá trình ăn mòn.

Bước đầu tiên của quá trình oxy hóa là loại bỏ tạp chất và chất gây ô nhiễm. Nó đòi hỏi bốn bước để loại bỏ chất hữu cơ, tạp chất kim loại và làm bay hơi nước dư. Sau khi làm sạch, tấm wafer có thể được đặt trong môi trường nhiệt độ cao từ 800 đến 1200 độ C và lớp silicon dioxide (tức là "oxit") được hình thành bởi dòng oxy hoặc hơi nước trên bề mặt tấm wafer. Oxy khuếch tán qua lớp oxit và phản ứng với silicon để tạo thành lớp oxit có độ dày khác nhau và độ dày của nó có thể được đo sau khi quá trình oxy hóa hoàn tất.

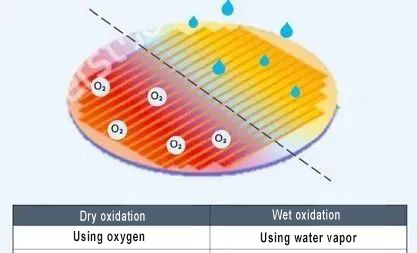

Quá trình oxy hóa khô và quá trình oxy hóa ướt Tùy thuộc vào các chất oxy hóa khác nhau trong phản ứng oxy hóa, quá trình oxy hóa nhiệt có thể được chia thành quá trình oxy hóa khô và quá trình oxy hóa ướt. Loại thứ nhất sử dụng oxy tinh khiết để tạo ra lớp silicon dioxide, tuy chậm nhưng lớp oxit mỏng và đậm đặc. Loại thứ hai cần cả oxy và hơi nước hòa tan cao, được đặc trưng bởi tốc độ tăng trưởng nhanh nhưng lớp bảo vệ tương đối dày với mật độ thấp.

Ngoài chất oxy hóa, còn có các biến số khác ảnh hưởng đến độ dày của lớp silicon dioxide. Đầu tiên, cấu trúc wafer, các khuyết tật bề mặt và nồng độ pha tạp bên trong của nó sẽ ảnh hưởng đến tốc độ tạo ra lớp oxit. Ngoài ra, áp suất và nhiệt độ do thiết bị oxy hóa tạo ra càng cao thì lớp oxit được tạo ra càng nhanh. Trong quá trình oxy hóa cũng cần sử dụng tấm giả theo vị trí của wafer trong thiết bị để bảo vệ wafer và giảm sự chênh lệch về mức độ oxy hóa.

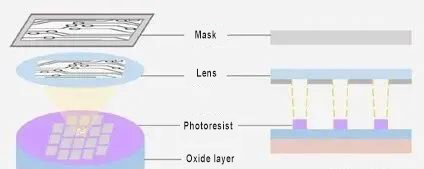

Bước 3: Quang khắc

Quang khắc là để "in" mẫu mạch lên tấm bán dẫn thông qua ánh sáng. Chúng ta có thể hiểu nó giống như việc vẽ bản đồ mặt phẳng cần thiết cho việc sản xuất chất bán dẫn lên bề mặt tấm wafer. Độ mịn của mẫu mạch càng cao thì khả năng tích hợp của chip thành phẩm càng cao, điều này phải đạt được nhờ công nghệ quang khắc tiên tiến. Cụ thể, quang khắc có thể được chia thành ba bước: phủ chất quang dẫn, phơi sáng và phát triển.

Lớp phủ

Bước đầu tiên của việc vẽ mạch điện trên tấm bán dẫn là phủ chất quang dẫn lên lớp oxit. Photoresist làm cho tấm bán dẫn trở thành "giấy ảnh" bằng cách thay đổi tính chất hóa học của nó. Lớp quang điện trên bề mặt của tấm wafer càng mỏng thì lớp phủ càng đồng đều và mẫu in được càng mịn. Bước này có thể được thực hiện bằng phương pháp "quay phủ". Theo sự khác biệt về khả năng phản ứng ánh sáng (tia cực tím), chất quang dẫn có thể được chia thành hai loại: dương và âm. Phần trước sẽ phân hủy và biến mất sau khi tiếp xúc với ánh sáng, để lại họa tiết của vùng không được phơi sáng, trong khi phần sau sẽ polyme hóa sau khi tiếp xúc với ánh sáng và làm cho họa tiết của phần tiếp xúc xuất hiện.

Phơi bày

Sau khi màng quang điện được phủ lên tấm bán dẫn, quá trình in mạch có thể được hoàn thành bằng cách kiểm soát mức độ tiếp xúc với ánh sáng. Quá trình này được gọi là "tiếp xúc". Chúng ta có thể truyền ánh sáng một cách có chọn lọc qua thiết bị phơi sáng. Khi ánh sáng đi qua mặt nạ chứa mẫu mạch, mạch có thể được in trên tấm bán dẫn được phủ màng quang điện bên dưới.

Trong quá trình phơi sáng, mẫu in càng mịn thì chip cuối cùng có thể chứa được càng nhiều linh kiện, giúp nâng cao hiệu quả sản xuất và giảm giá thành của từng linh kiện. Trong lĩnh vực này, công nghệ mới hiện đang thu hút nhiều sự quan tâm là kỹ thuật in thạch bản EUV. Tập đoàn nghiên cứu Lam đã cùng phát triển công nghệ quang điện màng khô mới với các đối tác chiến lược ASML và imec. Công nghệ này có thể cải thiện đáng kể năng suất và hiệu suất của quá trình phơi sáng in thạch bản EUV bằng cách cải thiện độ phân giải (yếu tố then chốt trong việc tinh chỉnh độ rộng mạch).

Phát triển

Bước sau khi tiếp xúc là phun chất hiện hình lên tấm wafer, mục đích là loại bỏ chất quang dẫn ở vùng không được che phủ của mẫu, để có thể lộ ra mẫu mạch in. Sau khi quá trình phát triển hoàn tất, nó cần được kiểm tra bằng nhiều thiết bị đo lường và kính hiển vi quang học khác nhau để đảm bảo chất lượng của sơ đồ mạch.

Bước 4: Khắc

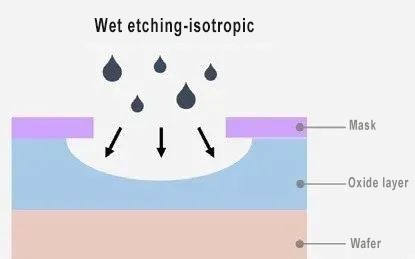

Sau khi hoàn thành quá trình quang khắc sơ đồ mạch trên tấm bán dẫn, quy trình khắc axit được sử dụng để loại bỏ bất kỳ màng oxit dư thừa nào và chỉ để lại sơ đồ mạch bán dẫn. Để làm điều này, chất lỏng, khí hoặc plasma được sử dụng để loại bỏ những phần dư thừa đã chọn. Có hai phương pháp khắc chính, tùy thuộc vào chất được sử dụng: khắc ướt bằng dung dịch hóa học cụ thể để phản ứng hóa học nhằm loại bỏ màng oxit và khắc khô bằng khí hoặc plasma.

khắc ướt

Khắc ướt sử dụng dung dịch hóa học để loại bỏ màng oxit có ưu điểm là chi phí thấp, tốc độ ăn mòn nhanh và năng suất cao. Tuy nhiên, khắc ướt là đẳng hướng, nghĩa là tốc độ của nó theo mọi hướng là như nhau. Điều này khiến mặt nạ (hoặc màng nhạy cảm) không được căn chỉnh hoàn toàn với màng oxit bị ăn mòn, do đó rất khó xử lý các sơ đồ mạch rất tinh xảo.

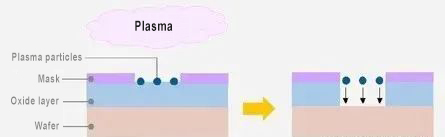

khắc khô

Khắc khô có thể được chia thành ba loại khác nhau. Đầu tiên là khắc hóa học, sử dụng khí ăn mòn (chủ yếu là hydro florua). Giống như khắc ướt, phương pháp này là đẳng hướng, có nghĩa là nó không phù hợp để khắc tinh.

Phương pháp thứ hai là phún xạ vật lý, sử dụng các ion trong plasma để tác động và loại bỏ lớp oxit dư thừa. Là một phương pháp khắc dị hướng, khắc phún xạ có tốc độ ăn mòn khác nhau theo hướng ngang và dọc nên độ mịn của nó cũng tốt hơn so với khắc hóa học. Tuy nhiên, nhược điểm của phương pháp này là tốc độ ăn mòn chậm do phụ thuộc hoàn toàn vào phản ứng vật lý do va chạm ion.

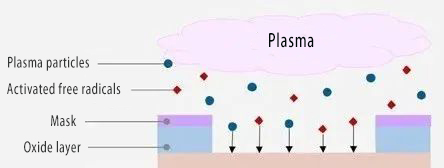

Phương pháp thứ ba cuối cùng là khắc ion phản ứng (RIE). RIE kết hợp hai phương pháp đầu tiên, nghĩa là trong khi sử dụng plasma để khắc vật lý ion hóa, khắc hóa học được thực hiện với sự trợ giúp của các gốc tự do được tạo ra sau khi kích hoạt plasma. Ngoài tốc độ khắc vượt quá hai phương pháp đầu tiên, RIE có thể sử dụng các đặc tính dị hướng của các ion để đạt được khả năng khắc mẫu có độ chính xác cao.

Ngày nay, phương pháp khắc khô đã được sử dụng rộng rãi để cải thiện hiệu suất của các mạch bán dẫn tốt. Việc duy trì tính đồng nhất của quá trình khắc toàn bộ tấm wafer và tăng tốc độ khắc là rất quan trọng và thiết bị khắc khô tiên tiến nhất hiện nay đang hỗ trợ sản xuất các chip nhớ và logic tiên tiến nhất với hiệu suất cao hơn.

VeTek Semiconductor là nhà sản xuất chuyên nghiệp của Trung Quốc vềLớp phủ cacbua tantali, Lớp phủ silicon cacbua, Than chì đặc biệt, Gốm sứ cacbua silicVàGốm sứ bán dẫn khác. VeTek Semiconductor cam kết cung cấp các giải pháp tiên tiến cho các sản phẩm wafer SiC khác nhau cho ngành bán dẫn.

Nếu bạn quan tâm đến các sản phẩm trên, xin vui lòng liên hệ trực tiếp với chúng tôi.

Đám đông: +86-180 6922 0752

WhatsAPP: +86 180 6922 0752

Email: anny@veteksemi.com